Џo“TЃFANALOG DEVICES ҺР

http://designtools.analog.com/dt/sdtutorial/sdtutorial.html

| Ѓ@ |

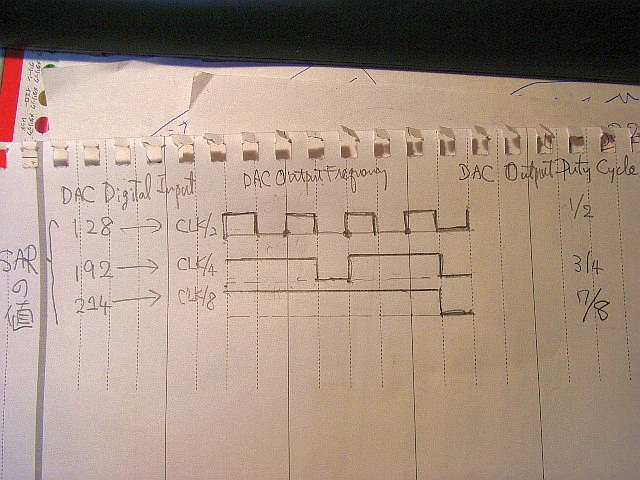

| Ѓ@‚PЃD‚±‚к‚ҒЃAѓұѓ°-ADC‚МЊө—қ‚Е‚·‚Л Ѓ@Ѓ@Ѓ@Ѓ@ANALOG DEVICESҺР‚МDesignTools“а‚ЕЃA‘fђ°‚з‚µ‚ұTool‚рЃAЊ©‚В‚Ү‚Ь‚µ‚ҢЃB Ѓ@Ѓ@Ѓ@Ѓ@‚Ё‰A—l‚ЕЃAѓұѓ°-ADC‚МЊө—қ‚ҒЃA‰р‚Б‚Д‚«‚Ь‚µ‚ҢЃAЃ@tnx to ANALOG DEVICESҺР Ѓ@Ѓ@Ѓ@Ѓ@Џ]‚Б‚ДЃAScilabЃAMaxima‚НЃA‚Ё‹x‚Э‚µ‚Ь‚·ЃB Ѓ@Ѓ@Ѓ@Ѓ@MAXIMҺР‚аЃA—L‰v‚И•¶Џ‘‚рЊцЉJ‚µ‚Д‚‚к‚Д‚ұ‚Ь‚·ЃB Џo“TЃFhttp://www.maxim-ic.com/appnotes.cfm/an_pk/1080/ Ѓ@Ѓ@Ѓ@Ѓ@‚Ң‚ңЃADAC‚Й•t‚ұ‚Д‚НЃA‚mѓrѓbѓgDAC‚рҺg‚Б‚Д‚ұ‚Ь‚·ЃB Џo“TЃFЏг‚Й“Ү‚¶ €к•ыЃALatticeҺР‚МRD1063.pdf‚Е‚НЃADeltaSigma-DAC‚рҺg‚Б‚Д‚ұ‚Ь‚·ЃA‚±‚±‚Ғђ¦‚ұ‚Ж‚±‚л‚Е‚·ЃB Ѓ@Ѓ@Ѓ@Ѓ@‚±‚к‚ҒЃA‚З‚¤€б‚¤‚©‚ЖЊң‚¤‚Ж Ѓ@Ѓ@Ѓ@Ѓ@DeltaSigma-DAC‚Е‚НЃA Ѓ@Ѓ@Ѓ@Ѓ@  Ѓ@Ѓ@Ѓ@Ѓ@DAC‚МOutput‚рЃA Ѓ@Ѓ@Ѓ@Ѓ@DAC‚Й‘—‚з‚к‚Д‚‚йSAR‚М’l‚Й‚ж‚Б‚ДЃA Ѓ@Ѓ@Ѓ@Ѓ@DACЃ@Output Frequency‚ЖЃADACЃ@Output Duty Cycle ‚р“ҮҺһ‚Й•П‰»‚і‚№‚Д Ѓ@Ѓ@Ѓ@Ѓ@1bit‚Е•\Њ»‚µ‚Д‚µ‚Ь‚¤ЃA‚ЖЊң‚¤ђ¦‚і‚Е‚·ЃB Ѓ@Џo“TЃFLatticeҺР‚МRD1063.pdf Ѓ@Ѓ@Ѓ@Ѓ@‚»‚к‚ЖЃ@Successive Approximation Resister‚М–рЉ„‚И‚М‚Е‚·‚Ғ Ѓ@Ѓ@Ѓ@Ѓ@Analog Input Signal ‚Ғ€к’и‚ң‚Ж‚·‚й‚ЖЃA Ѓ@Ѓ@Ѓ@Ѓ@‚±‚к‚рЃA‚Q•Ғ–Ш‚Й‚ДЃA€к‚В€к‚ВЃAInput Signal‚ж‚иЃA‘е‚«‚ұЃAЏ¬‚і‚ұ‚Ж”дЉr‚µ‚И‚Ғ‚зЃA Ѓ@Ѓ@Ѓ@Ѓ@ҚЕЏI“I‚ЙЃASAR‚ЕЊ€‚Я‚з‚к‚Ңѓrѓbѓgђ”‚ЕЃA‹ЯҺ—‚µ‚ДҚs‚‚з‚µ‚ұ‚М‚Е‚·ЃB Ѓ@Ѓ@Ѓ@Ѓ@Џ‰‚Я‚Д’m‚и‚Ь‚µ‚ҢЃA‚¤‚к‚µ‚ұ‚ИЃ@ЃфЃ@Ѓ@Ѓ@Ѓ@Tnx to Lattice SemiconductorҺР Џo“TЃFLatticeҺР‚МRD1063.pdf Ѓ@Ѓ@Ѓ@Ѓ@‚¤Ѓ[Ѓ[‚с...Ѓ@Ѓ@Һ„‚Й‚Е‚«‚й‚©‚З‚¤‚©ЃA‘S‚‚н‚©‚и‚Ь‚№‚с‚ҒЃA Ѓ@Ѓ@Ѓ@Ѓ@LatticeҺР‚М‚Ё‰A‚р‚а‚ү‚Ь‚µ‚ДЃAЏo—€‚»‚¤‚И‹C‚Ғ‚µ‚Д‚«‚Ь‚µ‚ҢЃA‚н‚сЃB. Ѓ@Ѓ@Ѓ@Ѓ@ H.21.12.8 |

| Ѓ@ |