入力 1Hzでも、出力は正常です。(積分器 ynは、既に飽和しています)

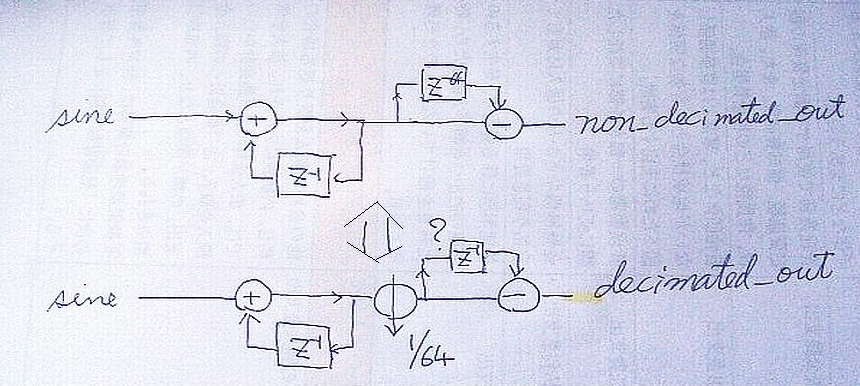

| 1.本物のCICフィルタかどうか、解りませんが... 今回は、cascadeする前の、1段のSINCフィルタについて比較しました。  non_decimated_out : SINCフィルタ。 decimated_out : SINCフィルタの間に、decimationを行ったもの。 この両者の比較です。 decimation比率は 64に固定。 inputのsin波は、10bit。 sine波のsamplingは、fs=56.8MHz (元クロックの周波数/2、 7.1MHz*8) 先ず、積分器(yn)のbit数が 16の時 decimated_outが、正しい波形になりません。(sineが、1KHz入力波形) |

decimateする事を前提に、SINCフィルタを調べていますから、アウトです。 次は、積分器のbit数が17の時 積分器(yn)は、完全に飽和しまくりですが、decimated_outの出力は正常です。 よって、以降の実験では、積分器のbit数は、17に固定します。 1KHz入力と、10KHz入力の比較 10Hz入力 10Hz,100Hz、1KHz入力の比較 周波数が違っても、入力の振幅が同じなら、同じ振幅で出力される模様です。 1KHz、10KHz入力の比較 上図の拡大 decimate比率が1/64と、大きいので、10KHz出力は、ギザギザしてきました。( fs/M =56.8MHz/64=887.5KHz ) 最後は、入力が1Hzの時です(冒頭の図がそれにあたります、再掲) このsimulationは、40分近くかかった模様です。(あきらめて、買い物に出かけてしまいましたので、推測です (^_^;; ) simulationでは、1Hz付近でも正確に出力されますので、安心ですね。 次回は、cascadeされた、所謂 CICフィルタを調べてみます。 果たして、積分器のbit数が、いくら必要になるのでしょうか..... H.22.7.14 |