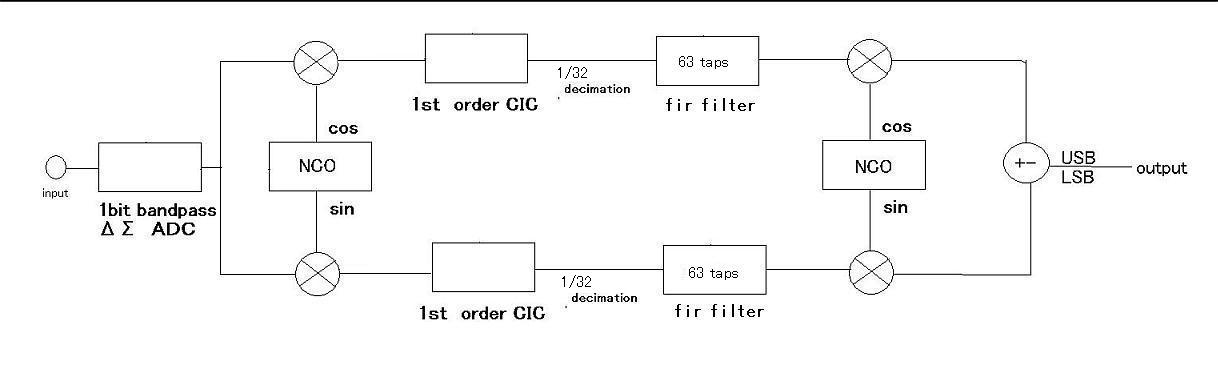

7000KHz input->ΔΣ-ADC->mix->182KHz->mix->1KHz 7000KHz input->ΔΣ-ADC->mix->182KHz->CIC & fir LPF->mix->1KHz

| 1.迷っています 前々節で、以下の構想を練りました。  その通りにすると、ノイズフロアが悪化して、高調波も問題になってくるのです。 反対に、 filterを一切通さない方が素直で、結果も優れています。 こんな感じです。 なんか、変。 しかしながら、1/1024 decimationの為に、CIC filterを通すと 7000KHz input->ΔΣ-ADC->mix->182KHz->mix->1KHz->CIC filter-> 7000KHz input->ΔΣ-ADC->mix->182KHz->CIC & fir LPF->mix->1KHz これやったら、 「CIC & fir LPFを通したもの」( 右側 )のほうが、結果がよいですね。 うーん、 decimationは、 fir filterで行ってもいいのですが、 decimation自体は、必ず必要なので、行わない訳には、いきません。 ほんま、困ったで...... 2.今回は、Xilinx社の Fir Compilerを、使ってみました 使い方が、間違っているかも知れません。 16 slice も、DSPに使うのは、勿体無い。 で、 Distributed Arithmeticにする。 一応、それらしく動いているようですが なんせ、LUTの消費が激しいです。 ベタ描きのほうが、いいかも........ H.22.12.26 |