前節で、帯域を3KHzに採りたいと言う希望がありました。

結局、fir係数の数は、25、又は、26でないと、H8-3664F(16MHz)では、不可能でした。

プログラムの工夫の限界では...

と、思いましたが、まだまだ、甘かった...

元の設計は

(Tech I ディジタル信号処理とDSP 三上直樹先生 付属のフィルタ設計ソフト)

他の設計ソフトを使うと (DSP処理のノウハウ 西村OM)

実測は

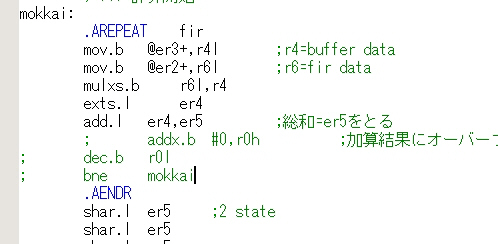

ここで、アセンブラの繰り返し展開 .AREPEAT .AENDRを使うと、スピードが約1.2倍に上がりました!

従って、firの係数の数を31まで上げる事ができました。

firの性能が、上がりました!(同一の設計条件で比較)

私は、まだまだ甘いです...(T_T)

これで、3694F(20MHz 動作)を使って、Q10でいけば、6dB帯域も採れるし、帯域外も40dB以上は採れそう...

いずれにしても、H8 3664F(16MHZ)では、苦しいですね...

まだまだ、甘い!

ベストテクノロジー社 から

3694F(20MHz 動作)が、まもなく発売されるそうです。

これですと、fir係数も30以上採れそうで、もっと、よくなると思います...

でも、SSBの作り方の基本は、全く同じですね。

SH2(SH7047F)も考えているのですが、フリーの開発環境、HEW2を使えなくなります。

SH7047を、開発環境込みで販売していますが...

(15インチ液晶モニタが、充分買えるやんか... よく、考えてみようっと...)

ここの開発環境は、アセンブラもできて、いいのですが..思案のしどころです,hi。

愈々、信号の複素化を調べて行きます。

難しそうや...

H.15.11.6

This document created by Scientific Notebook 4.1. この文書は次の製品で作成しました Scientific Notebook 4.1.