| 1.56.8MHzのサンプリング周波数では、駄目そう |

| 7MHzの信号を、75tapsのfir filterに通す -> filtered

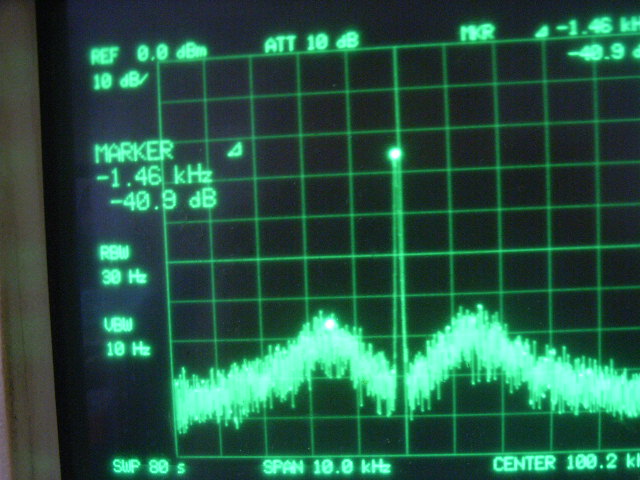

7MHzの信号と、7.1MHz(NCO)の、1bit信号同士の積を計算する。 これを、行おうとしましたが、アウト! たった、75tapsのfir filterを通すだけで、FPGAで動作できなくなる..... これでは、アカンな....... で、どうするか? 2.decimationが必要 計算のためのクロックは、113.6MHzと、高くしておいて サンプリング周波数の方を下げる(decimation) ->計算の時間に、余裕ができる。 そんな、勘定を目論んでいます。 decimationとは、データを間引く事ですね。 そんで、単純に、間引く事をやってみました。 尚、間引くデータは、7MHzと、7.1MHz sin波を、既に掛けたものを対象にしています。 この際、ノイズの盛り上がりには、目をつぶりましょうね。 (ハードウェアで解決できるかも)  先ずは、decimation無しの場合 次に、56.8MHzを半分にdecimation 56.8MHzの1/3のdecimation 56.8MHzの1/6のdecimation ご覧のように、 decimationの結果は、1、1/2、1/3、1/6と、分母の数を増す毎に 100KHz出力と、ノイズレベルとの差は、小さくなります。 100KHz出力のピークは、一定なのですが、 ノイズレベルの方が、ぐんぐんと、上がって行きます、ぐんぐん..... とほほ (-_-;; これは、正しいdecimationでは、無いですね。 で、色々探っていますが、ホロン様のHPを拝見して、解決できそうな気が、してきました、御礼。 H.22.6.8 |