|

1.さて、困った....

1st

order CIC filterならば、1/600 まで、decimationできたのですが

2nd order

になると、困った事が発生しました。

1/32

decimation までは、至極 正常でした。

ですが、1/64

decimationになると

正常な状態と、そうでない状態が、1秒位毎に、交互に発生します。

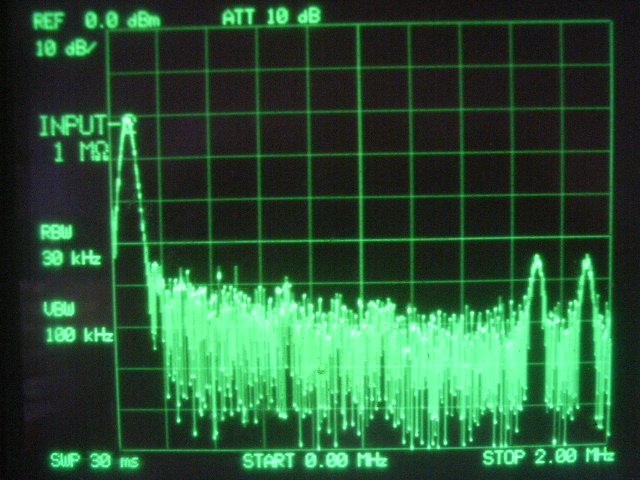

正常な状態: 1/64

decimation using 2nd order CIC filter

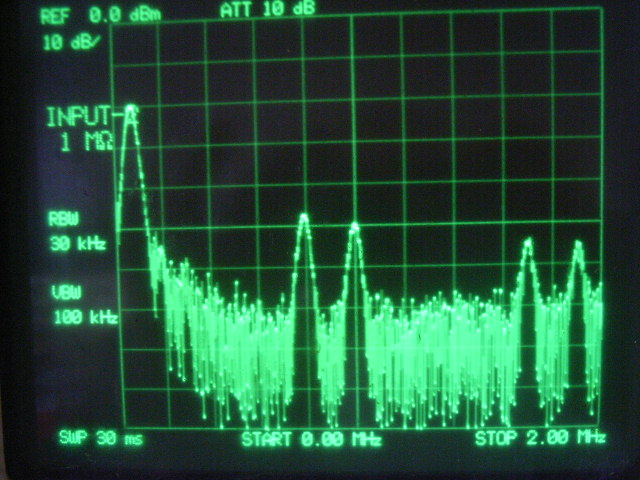

正常でない状態: 1/64 decimation

using 2nd order CIC

filter

つまり、不安定な状態が発生するのです、困ったぞ.....

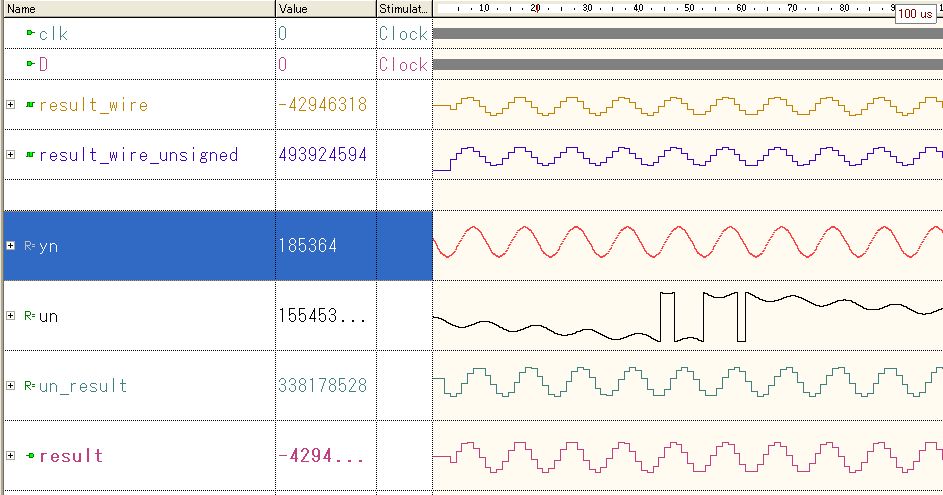

2nd order CIC fiter の moduleは、これでいいと思っているのですが....

module

cic_filter_2nd_order(clk,data_input,result);

//decimation ratio =1/R

parameter R=64;

input clk;

input signed[17:0]data_input;

output reg signed[29:0]result;

reg signed[27:0]yn=0;

reg signed[32:0]yn_1=0;

reg signed[32:0]z[1:0];

reg signed[32:0]un=0;

reg signed[32:0]un_1=0;

reg signed[32:0]un_z[1:0];

reg signed[32:0]un_result=0;

reg [10:0]decim_count=0;

always@(posedge clk) begin

//integrator

yn=yn_1+data_input;

yn_1=yn;

un=un_1+yn;

un_1=un;

//decimation

decim_count=decim_count+1;

if(decim_count==R) begin

//differentiator

un_z[1]=un_z[0];

un_z[0]=un;

un_result=un_z[0]-un_z[1];

z[1]=z[0];

z[0]=un_result;

result=z[0]-z[1];

decim_count=0;

end

end

endmodule

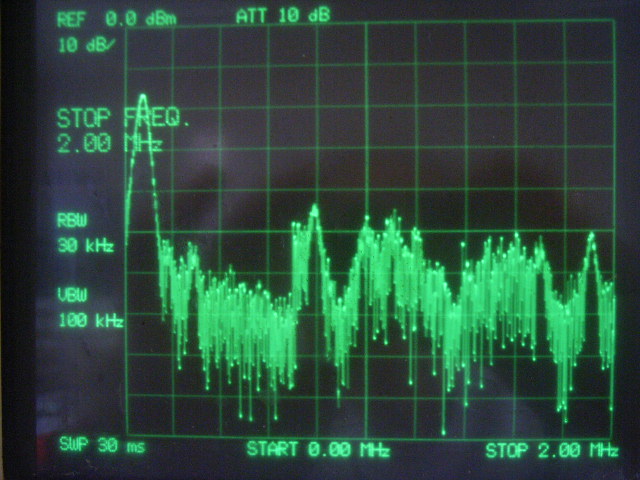

functional simulationも、問題ないと、思います。

ひとつ考えられる事は、

私の採っているDA変換は、Pulse Density

Modulation方式です。

以下のような構造ですので、時間がかかるのです。

module

PDM(clk,VDA,cy_out);

parameter

DATA_WIDTH2=18;

input clk;

input

[DATA_WIDTH2-1:0] VDA;

output cy_out;

///// internal variables

////////

reg [DATA_WIDTH2-1:0] R=0;

reg cy=0;

assign cy_out= cy;

always @(posedge clk) begin

{cy,R} <=R+

VDA;

end

endmodule

このPDMに要する時間と、CIC filterで要する時間との タイミングのズレでは、ないのかなと........discrepancy

2nd order CIC filter の積分と、微分を、

always@(posedge clk) begin

//integrator

yn=yn_1+data_input;

yn_1=yn;

un=un_1+yn;

un_1=un;

//differentiator

un_z[1]=un_z[0];

un_z[0]=un;

un_result=un_z[0]-un_z[1];

//decimation

decim_count=decim_count+1;

if(decim_count==R) begin

//differentiator

z[1]=z[0];

z[0]=un_result;

result=z[0]-z[1];

decim_count=0;

end

微分の一部を、decimation部分から、除外して上記のように配置にすれば、

完全に作動するのですが

これでは、理屈的に、1st

order

CICと、変わりませんねえ......

積分して、微分 -> 元に戻るだけ

しっかし、冒頭の 1st order CIC filter

の効果は、優れています。

ADC自体が bandpass filterを、通していますので

1st

order CIC

filterで、充分かもしれません。

と、苦しい言い訳...... (^_^;;

H.22.9.9 |