|

1.なんとか、トラブル解消しました

2nd

order CIC filter

の場合、トラブルの原因は

最初の積分器である、ynのビット数不足でした。

これを増やしてやる事によって、不安定な状態が解消されました。

module

cic_filter_2nd_order(clk,data_input,result);

//decimation ratio =1/R

parameter R=1000;

parameter OUTPUT_WIDTH=36;

input clk;

input

signed[17:0]data_input;

output signed[OUTPUT_WIDTH:0]result;

reg signed[OUTPUT_WIDTH:0]result_reg;

reg signed[OUTPUT_WIDTH:0]yn=0;

reg signed[OUTPUT_WIDTH:0]yn_1=0;

reg

signed[OUTPUT_WIDTH:0]z[1:0];

reg signed[46:0]un=0;

reg signed[OUTPUT_WIDTH:0]un_1=0;

reg

signed[OUTPUT_WIDTH:0]un_z[1:0];

reg signed[OUTPUT_WIDTH:0]un_result=0;

reg [10:0]decim_count=0;

assign result=result_reg;

always@(posedge clk) begin

//integrator

yn=yn_1+data_input;

yn_1=yn;

un=un_1+yn;

un_1=un;

//decimation

decim_count=decim_count+1;

if(decim_count==R)

begin

//differentiator

un_z[1]=un_z[0];

un_z[0]=un;

un_result=un_z[0]-un_z[1];

z[1]=z[0];

z[0]=un_result;

result_reg=z[0]-z[1];

decim_count=0;

end

end

endmodule

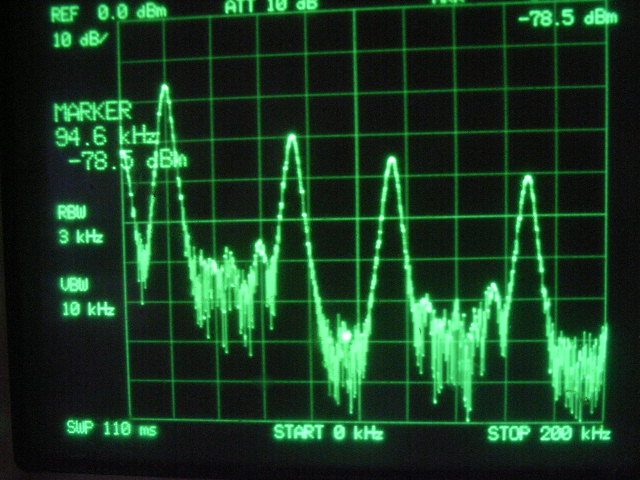

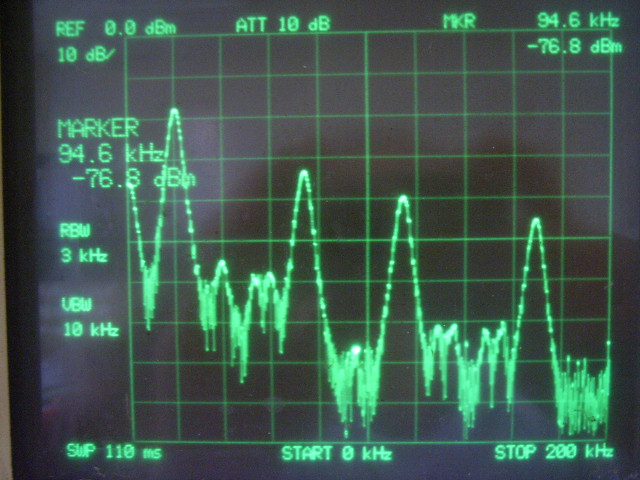

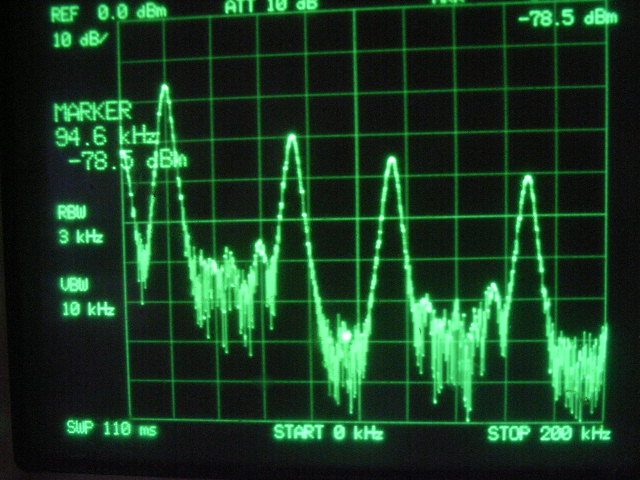

気になるのは、

1st order CIC と 2nd order

CIC filter の 1/600decimationでの比較が

ほとんど、変わらん事です。

2nd order CIC

filter

1st order CIC filter

ですので、

私のシステム ( use 1bit bandpass delta sigma ADC

)では、

1st order CIC

filterが、ふさわしいのでは、ないだろうかと、思っています。

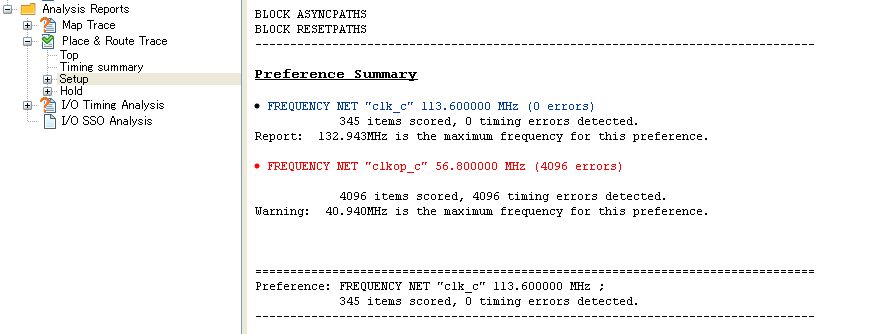

2.わからない所は

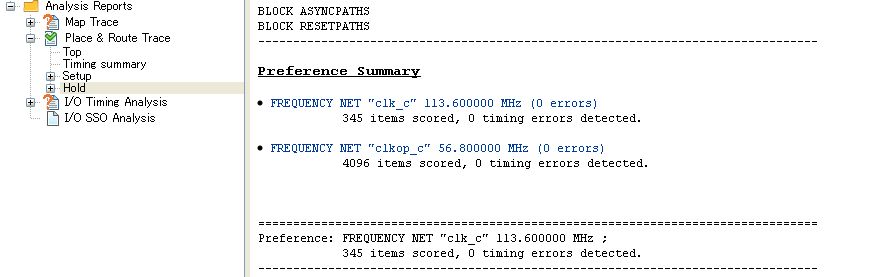

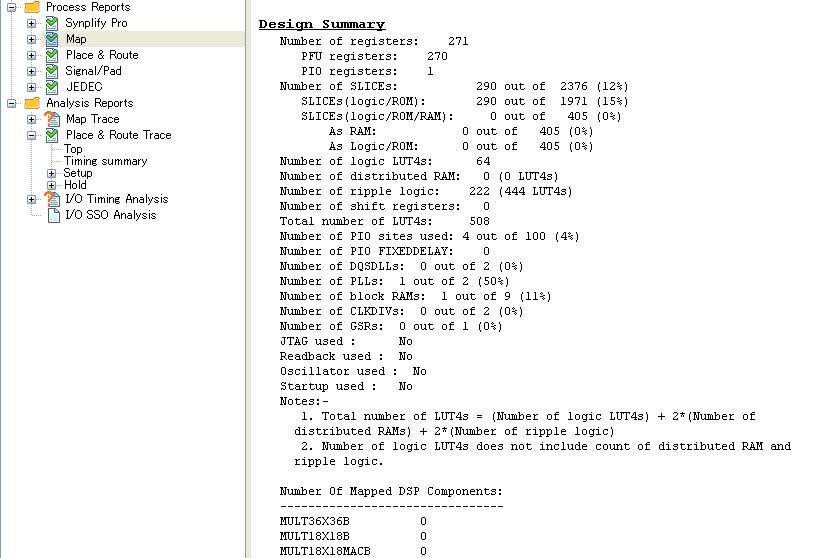

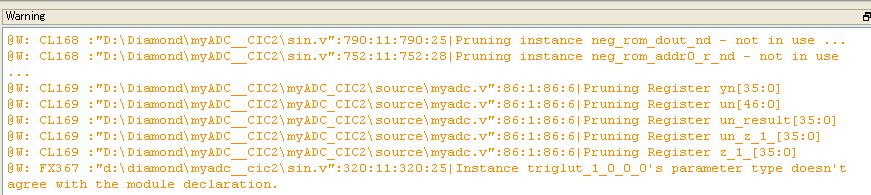

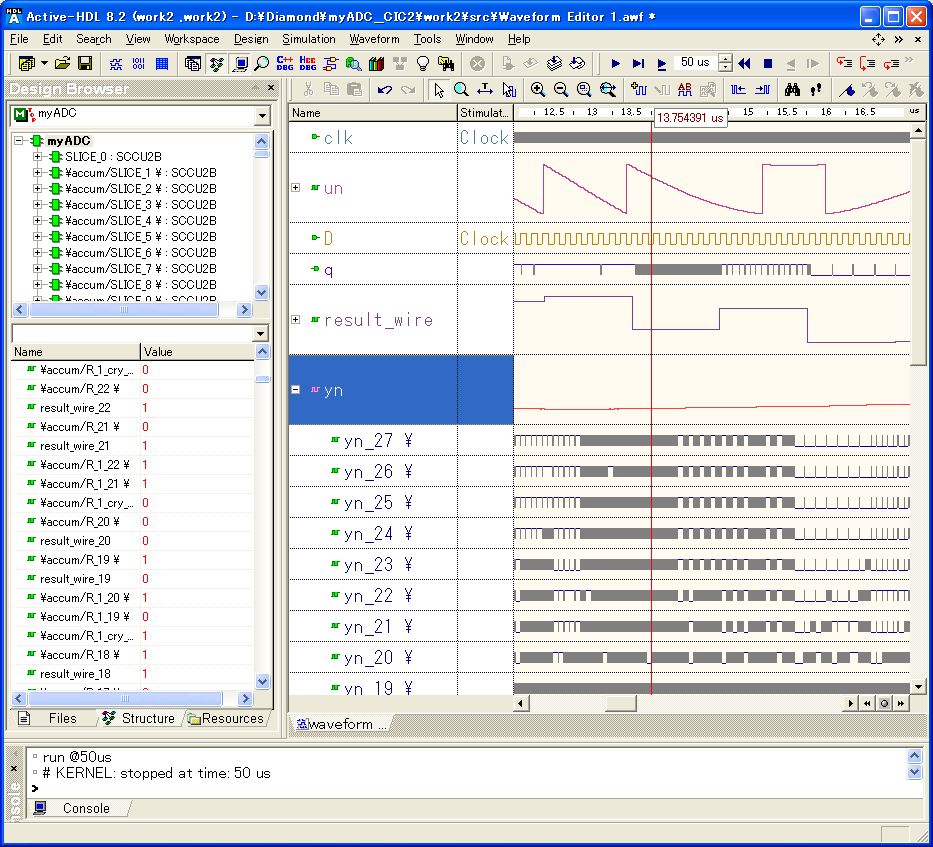

Lattice Diamond を使って、 buildすると、上記の2nd

order CIC filterでも

「まだ、ビット数が削れる」と、warninng が出ます。

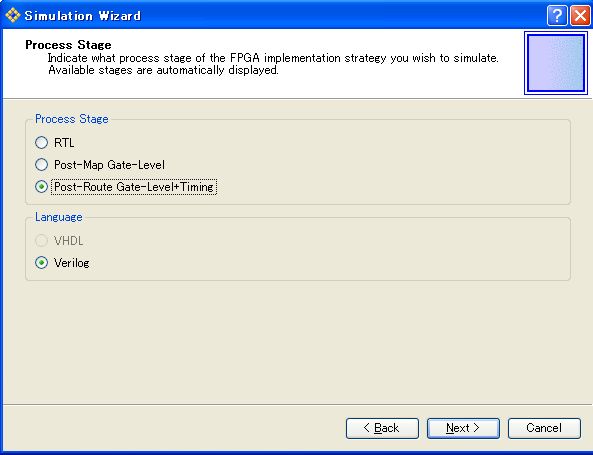

それで、「どう削ったのか?」を見る為に

Post-Route

Gate-Level+Timing の simulationを行いました。

これを見ますと、

yn[35:0] -->

yn[27:0]

まで、ビット数が減少されています。(他も、ビット数が減らされています。)

これを踏まえて

yn[27:0]

等、変更を加えて、buildすると、

これが、正しく、作動しません......

どうなってるんやろ

??

H.22.9.18

|